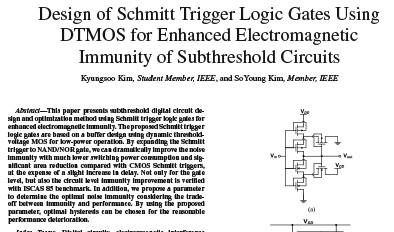

افزایش ایمنی الکترومغناطیسی پیشرفته مدارهای زیرآستانه با طراحی گیت های منطقی اشمیت تریگر منطقی با DTMOS

وقتی که ولتاژ منبع مدار کاهش یابد، ایمنی نویز برای تضمین یکپارچگی سیگنال مهمتر میشود. این مقاله یک روش بهبود ایمنی نویز کاربردی برای مدارهای زیرآستانه را ارائه میدهد. روش مرسوم برای افزایش ایمنی استفاده از یک اشمیتتریگر است که نیاز به یک مسیر جریان اضافی برای تنظیم ولتاژ آستانه سوئیچینگ دارد و حجم زیادی اشغال میکند. اگرچه، با استفاده از طرح VTMOS پیشنهادی، که ولتاژ آستانه ترانزیستورهای MOS را برای اجرای هیسترزیس ویژگیهای انتقال تنظیم میکند، هم منطقه و هم توان مصرفی میتواند به مقدار قابلتوجهی کاهش یابد و زمانیکه بهطور همزمان ایمنی نویز بهبود یافته، افزایش ناچیز در تاخیر، ایجاد می گردد. بنابرین، VTCMOS بر اساس طراحی منطقی دیجیتال میتواند طراحی IC کمتوان و مصونیت از نویز را فراهم سازد.